TPU7x (Ironwood)

Esta página descreve a arquitetura e as configurações disponíveis para a TPU7x, a TPU mais recente disponível no Google Cloud. O TPU7x é o primeiro lançamento na família Ironwood,o TPU de sétima geração. Google CloudA geração Ironwood foi concebida para a inferência e a preparação de IA em grande escala.

Com uma área de 9216 chips por pod, a TPU7x partilha muitas semelhanças com a TPU v5p. A TPU7x oferece um elevado desempenho para modelos densos e de grande escala, pré-preparação, amostragem e inferência com descodificação intensiva.

Para usar a TPUv7, tem de usar o Google Kubernetes Engine (GKE). Para mais informações, consulte o artigo Acerca das TPUs no GKE.

Também pode usar a TPU7x e o GKE com o TPU Cluster Director. O Cluster Director de TPUs está disponível através de uma reserva no modo de capacidade total, que lhe dá acesso total a toda a capacidade reservada (sem restrições) e visibilidade total da topologia de hardware, do estado de utilização e do estado de funcionamento das TPUs. Para mais informações, consulte a vista geral do modo de capacidade total.

Para aceder à TPU7x, contacte a equipa da sua conta.

Arquitetura do sistema

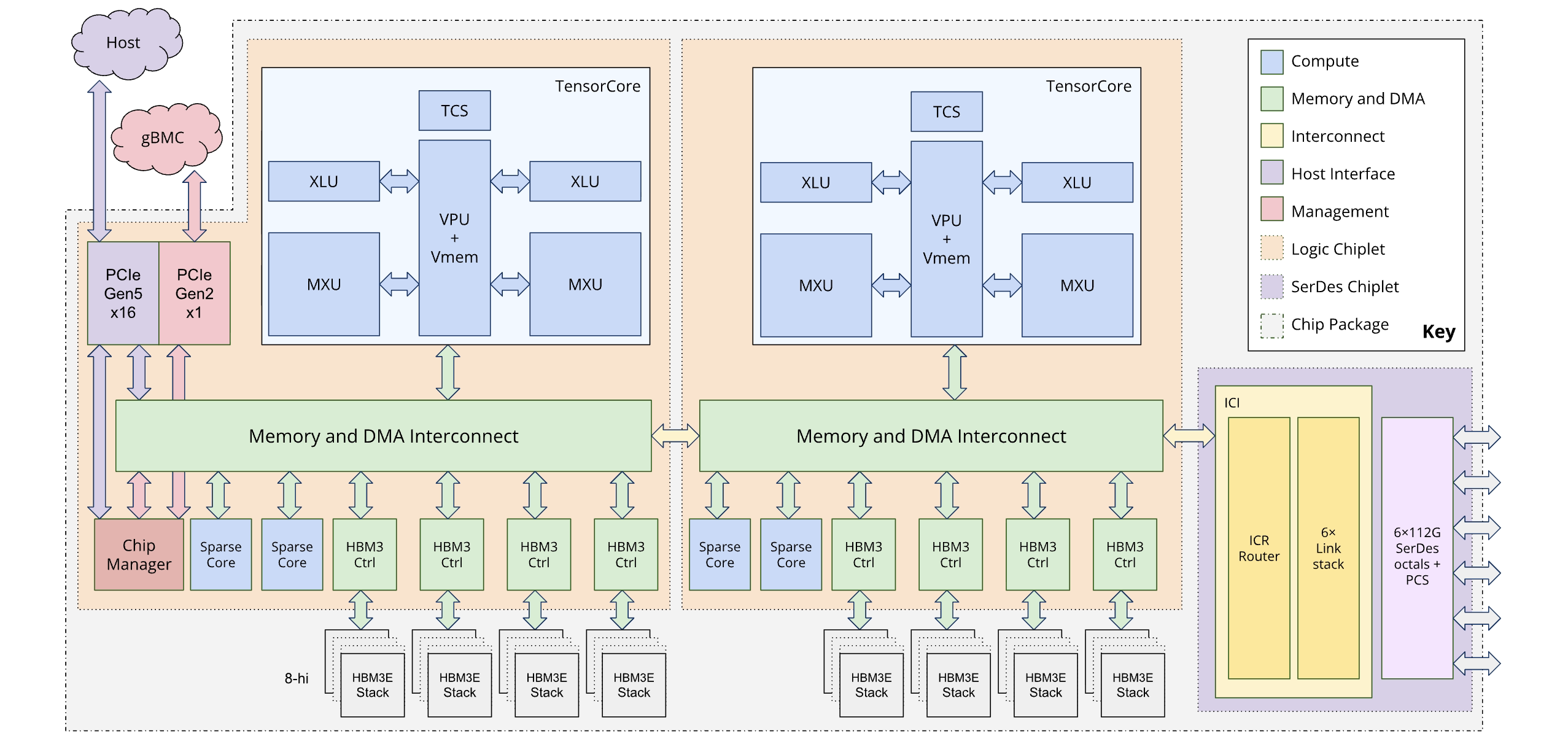

Cada chip TPU7x contém dois TensorCores e quatro SparseCores. A tabela seguinte mostra as principais especificações e os respetivos valores para a TPU7x em comparação com as gerações anteriores.

| Especificação | v5p | v6e (Trillium) | TPU7x (Ironwood) |

|---|---|---|---|

| Número de chips por agrupamento | 8960 | 256 | 9216 |

| Pico de computação por chip (BF16) (TFLOPs) | 459 | 918 | 2307 |

| Pico de cálculo por chip (FP8) (TFLOPs) | 459 | 918 | 4614 |

| Capacidade de HBM por chip (GiB) | 95 | 32 | 192 |

| Largura de banda da HBM por chip (GBps) | 2765 | 1638 | 7380 |

| Número de CPUs virtuais (VM de 4 chips) | 208 | 180 | 224 |

| RAM (GB) (VM de 4 chips) | 448 | 720 | 960 |

| Número de TensorCores por chip | 2 | 1 | 2 |

| Número de SparseCores por chip | 4 | 2 | 4 |

| Largura de banda de interligação entre chips (ICI) bidirecional por chip (GBps) | 1200 | 800 | 1200 |

| Largura de banda da rede do centro de dados (DCN) por chip (Gbps) | 50 | 100 | 100 |

O diagrama seguinte ilustra a arquitetura do Ironwood:

Arquitetura de dois chiplets

O modelo de programação Ironwood permite-lhe aceder a dois dispositivos TPU em vez da arquitetura de núcleo lógico único (também conhecido como MegaCore) usada nas gerações anteriores (TPU v4 e v5p). Esta alteração melhora a rentabilidade e a eficiência do fabrico do chip. Embora isto represente uma mudança arquitetónica, o novo design garante que pode reutilizar os modelos de software existentes com alterações mínimas.

As TPUs Ironwood são compostas por dois chiplets distintos. Isto representa uma mudança em relação ao espaço de memória unificado da arquitetura MegaCore.

Composição de chiplets: cada chiplet é uma unidade autónoma com um TensorCore, dois SparseCores e 96 GB de memória de largura de banda elevada (HBM).

Interligação de alta velocidade: os dois chiplets estão ligados por uma interface de matriz para matriz (D2D) seis vezes mais rápida do que um link de interligação entre chips (ICI) 1D. A comunicação entre chiplets é gerida através de operações coletivas.

Exposição da estrutura e do modelo de programação

O modelo de programação do Ironwood é semelhante ao das gerações de TPUs anteriores à v4, como a TPU v3. A nova arquitetura é exposta das seguintes formas:

Dois dispositivos por chip: as frameworks como o JAX expõem cada chip Ironwood como dois "dispositivos" separados, um para cada chiplet.

Topologia 4D: o JAX adiciona uma quarta dimensão à topologia para especificar qual dos dois dispositivos no chip usar. Isto permite-lhe usar modelos de software existentes com modificações mínimas.

Para mais informações sobre como alcançar um desempenho ideal com a arquitetura de dois chiplets, consulte o artigo Recomendações de desempenho para a arquitetura de dois chiplets do Ironwood

Configurações suportadas

Os chips TPU7x têm uma ligação direta aos chips vizinhos mais próximos em 3 dimensões, o que resulta numa malha 3D de ligações de rede. As fatias com mais de 64 chips são compostas por um ou mais "cubos" de chips de 4x4x4.

A tabela seguinte mostra formas de fatias 3D comuns suportadas para TPU7x:

| Topologia | Chips de TPU | Anfitriões | VMs | Cubos | Âmbito |

|---|---|---|---|---|---|

| 2x2x1 | 4 | 1 | 1 | 1/16 | Anfitrião único |

| 2x2x2 | 8 | 2 | 2 | 1/8 | Vários anfitriões |

| 2x2x4 | 16 | 4 | 4 | 1/4 | Vários anfitriões |

| 2x4x4 | 32 | 8 | 8 | 1/2 | Vários anfitriões |

| 4x4x4 | 64 | 16 | 16 | 1 | Vários anfitriões |

| 4x4x8 | 128 | 32 | 32 | 2 | Vários anfitriões |

| 4x8x8 | 256 | 64 | 64 | 4 | Vários anfitriões |

| 8x8x8 | 512 | 128 | 128 | 8 | Vários anfitriões |

| 8x8x16 | 1024 | 256 | 256 | 16 | Vários anfitriões |

| 8x16x16 | 2048 | 512 | 512 | 32 | Vários anfitriões |

VM TPU7x

Cada máquina virtual (VM) TPU7x contém 4 chips. Cada VM tem acesso a dois nós NUMA. Para mais informações acerca dos nós NUMA, consulte o artigo Acesso à memória não uniforme na Wikipédia.

Todas as fatias de TPU7x usam VMs de 4 chips de anfitrião completo. As especificações técnicas de uma VM TPU7x são:

- Número de vCPUs por VM: 224

- RAM por MV: 960 GB

- Número de nós NUMA por VM: 2

Hyperdisk

Por predefinição, o disco de arranque da VM para TPUv7 é o Hyperdisk Balanced. Pode anexar discos Hyperdisk Balanced adicionais à sua VM de TPU para armazenamento adicional.

Para mais informações sobre o Hyperdisk, consulte o artigo Vista geral do Hyperdisk. Para mais informações sobre as opções de armazenamento para o Cloud TPU, consulte o artigo Opções de armazenamento para dados do Cloud TPU.

O que se segue?

- Use TPUs v7 com o GKE

- Use a TPU7x com o TPU Cluster Director

- Use a Google Cloud plataforma de diagnósticos de ML para otimizar e diagnosticar as suas cargas de trabalho

- Execute uma carga de trabalho de treino usando uma receita otimizada para TPUv4

- Execute um microbenchmark da TPU7x